# **Specification**

# AGO 101J0-NN-N

# **REVISION STATUS**

| Revision | Description    | Page | Revision Date |

|----------|----------------|------|---------------|

| 1.0      | First Revision |      | 2018-07-05    |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

|          |                |      |               |

| Contents                        | Page |

|---------------------------------|------|

| 1.0. General Specification      | 4    |

| 2.0. Absolute Maximum Ratings   | 5    |

| 3.0. Optical characteristics    | 6    |

| 4.0. Block Diagram              | 10   |

| 5.0. Interface pin connection   | 11   |

| 6.0. Electrical characteristics | 13   |

| 7.0. Reliability test items     | 19   |

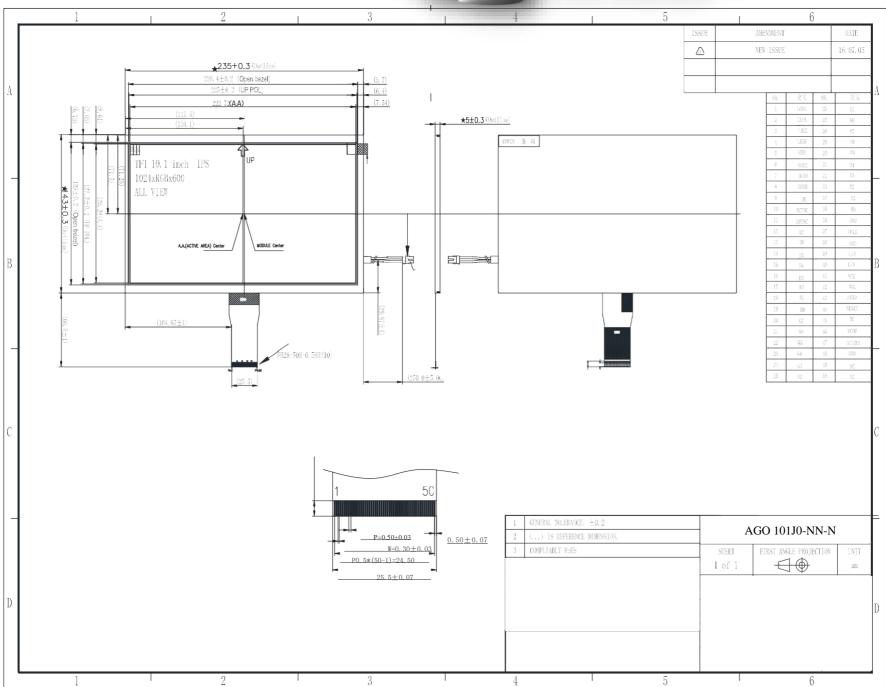

| 8.0. Outline dimension          | 20   |

| 9.0. Lot mark                   | 22   |

| 10.0. Package specification     | 23   |

| 11.0. General Precaution        | 24   |

# 1.0 GENERAL SPECIFICATION

#### 1.1 Introduction

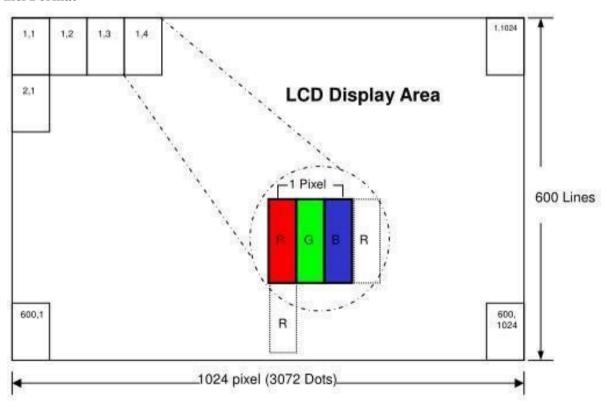

The model AGO 101JO-NN-N is a color active matrix thin film transistor (TFT) liquid crystal display without plagiarizer. This model is composed of amorphous silicon TFT as a switching device. This TFT LCD has a 10.1-inch wide (16:9) diagonally measured active display area with WVGA (1024 horizontal by 600 vertical pixel) resolution. Each pixel is divided into Red, Green, Blue dots which are arranged in vertical stripes.

#### 1.2 Features

10.1 inch configuration.

RGB interface

16.7M color by 8 bit R.G.B. signal input RoHS/Halogen Free

Compliance

#### 1.3Applications

Mobile

NB

Digital Photo frame

Display terminal for AV application

#### 1.4 General information

| Item              | Specification            | Unit     |

|-------------------|--------------------------|----------|

| Screen Size       | 10.1 inches              | Diagonal |

| Number of Pixel   | 1024 RGB (H) ×600(V)     | Pixels   |

| Display area      | 222.72(H) x 125.28(V)    | mm       |

| Outline Dimension | 235.0 x 143.0 x 5.0(Typ) | mm       |

| Display mode      | Normally Black           |          |

| Pixel arrangement | RGB Vertical stripe      |          |

| Pixel pitch       | 0.2175(H) ×0.2088(V)     | mm       |

| Back-light        | LED Side-light type      |          |

| Surface treatment | Anti - glare             |          |

| Interface         | TTL                      |          |

### 1.5 Mechanical Information

| Item        | Min.           | Тур.  | Max.  | Unit  |    |

|-------------|----------------|-------|-------|-------|----|

|             | Horizontal (H) | 234.7 | 235.0 | 235.3 | mm |

| Module Size | Vertical (V)   | 142.7 | 143.0 | 143.3 | mm |

|             | Depth (D)      | 4.7   | 5.0   | 5.3   | mm |

| Weig        |                | 300   | 320   | g     |    |

# 2.0 ABSOLUTE MAXIMUM RATINGS

#### 2.1 Electrical Absolute Rating

#### 2.1.1 TFT LCD Module

| ltem                 | Symbol | Min  | Max   | Unit | Note   |

|----------------------|--------|------|-------|------|--------|

| Power supply voltage | VDD    | -0.5 | 3.96  | V    | GND=0  |

|                      | AVDD   |      | 14.85 | V    | AGND=0 |

Note:

- 1. Stresses above those listed under" Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at indicated in the operational sections(6.1) of this specification.

- 2. Ta=25±2°C

## 2.2 Environment Absolute Rating

| Item                  | Symbol | Min. | Max. | Unit | Note |

|-----------------------|--------|------|------|------|------|

| Storage temperature   | Тѕтд   | -30  | 80   | °C   |      |

| Operating temperature | Topr   | -20  | 70   | °C   |      |

Note: If users use the product out off the environmental operation range(temperature and humidity), it will have visual quality concerns.

# 3.0 OPTICAL CHARACTERISTICS

# 3.1 Optical specification

| Item                          |       | Symbol           | Condition        | Min   | Type  | Max   | Unit     | Note      |

|-------------------------------|-------|------------------|------------------|-------|-------|-------|----------|-----------|

| White luminance<br>(Center)   |       | YL               |                  | 900   | 1000  |       | TBD nits | (1)(4)(6) |

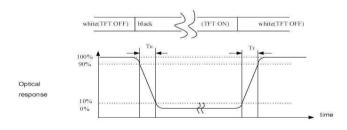

| D                             |       | $T_{\rm r}$      |                  |       | 10    | 20    |          | (1)(2)    |

| Response time                 |       | $T_{\mathrm{f}}$ |                  |       | 20    | 25    | msec     | (1)(3)    |

| Contrast ratio                |       | CR               | Θ=0              | 600   | 800   |       |          | (1)(2)    |

| Color                         |       |                  | Normal           | 0.260 | 0.310 | 0.360 |          | (1)(4)    |

| Chromaticity white (CIE 1931) | wnite | Wy               | Viewing<br>Angle | 0.280 | 0.330 | 0.380 |          | (1)(4)    |

|                               | II    | ΘL               |                  | 80    | 85    |       |          |           |

| <b>77</b>                     | Hor.  | ΘR               | CD 10            | 80    | 85    |       |          | (1)(4)    |

| Viewing Angle                 | ***   | ΘU               | CR 10            | 80    | 85    |       |          | (1)(4)    |

|                               | Ver.  | ΘD               |                  | 80    | 85    |       |          |           |

| Brightness                    |       | Buni             | Θ=0              | 80    |       |       | %        | (5)       |

| Color gamut (NTSC)            |       |                  | S                |       | 45    |       | %        |           |

| Optima View Direction         |       |                  | ALL VIEW         |       |       |       |          |           |

# 3.2 Measuring Condition

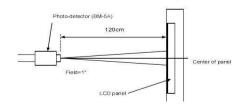

Measuring surrounding: dark room

LED current IL: 300mA

Ambient temperature: 25±2°C

30min. warm-up time

# 3.3 Measuring Equipment

BM-7 optical characteristics.

Measuring spot size: 20 ~ 21mm

#### Note (1) Definition of Viewing Angle

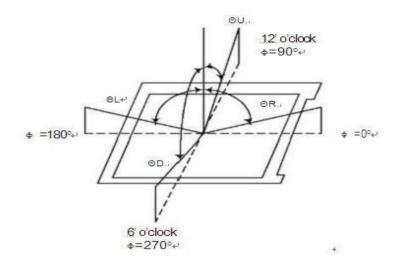

Viewing angle is the angle at which the contrast ratio is greater than 10. The viewing angles are determined for the horizontal or 3, 9 o"clock direction and the vertical or 6, 12 o"clock direction with respect to the optical axis which is normal to the LCD surface (see FIGURE 1).

Note (2) Definition of Contrast Ratio(CR): ✓ Measured at the center point of panel

CR=

∠

Luminance with all pixels white

Luminance with all pixels black

Note (3) Definition of Response Time: Sum of TR and T<sub>F</sub>

Note (4) Definition of optical measurement setup

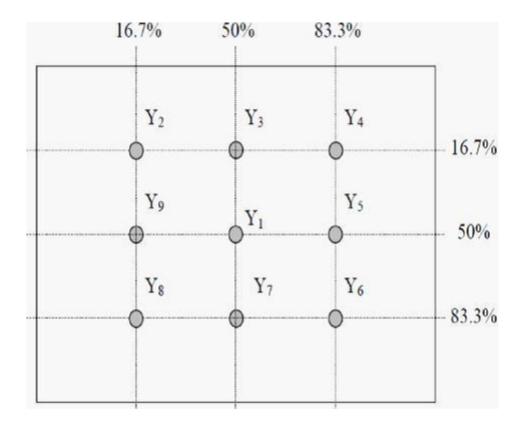

Note (5) Definition of brightness uniformity

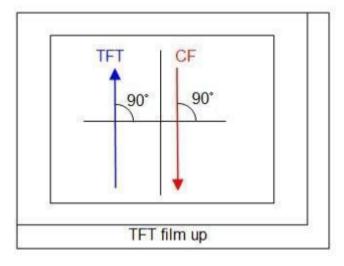

Note (6) Rubbing Direction (The different Rubbing Direction will cause the different optima view direction.

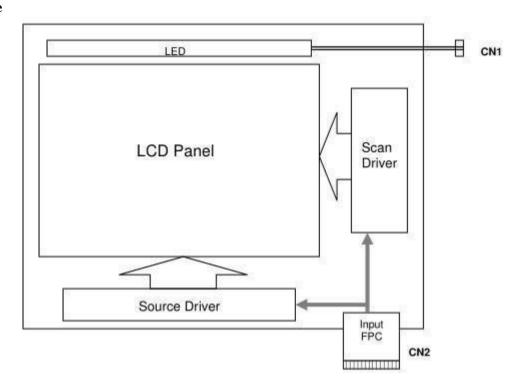

# 4.0 BLOCK DIAGRAM

#### **4.1 TFT LCD Module**

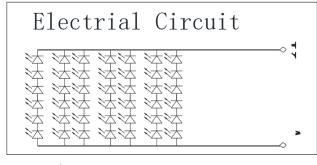

## **4.2 Pixel Format**

# 5.0 INTERFACE PIN CONNECTION

|         |        | , (FH28-50S-0.5SH (HIROSE), 50pin,pitch = 0.5mm)                    |        |

|---------|--------|---------------------------------------------------------------------|--------|

| Pin No. | Symbol | Function                                                            | Reamrk |

| 1       | LED+   | Power for LED back-light( Anode)                                    |        |

| 2       | LED+   | Power for LED back-light( Anode)                                    |        |

| 3       | LED-   | Power for LED back-light( Cathode)                                  |        |

| 4       | LED-   | Power for LED back-light( Cathode)                                  |        |

| 5       | GND    | Power Ground                                                        |        |

| 6       | VCOM   | Common Voltage                                                      |        |

| 7       | VDD    | Digital Power                                                       |        |

| 8       | MODE   | DE/SYNC Mode Select. Normally Pull High H :DE mode. L :HSD/VSD mode |        |

| 9       | DEN    | Date Enable signal                                                  |        |

| 10      | VSYNC  | Vertical sync input. Negative polarity                              |        |

| 11      | HSYNC  | Horizontal sync input. Negative polarity                            |        |

| 12      | В7     | Blue Data Input(MSB)                                                |        |

| 13      | В6     | Blue Data Input                                                     |        |

| 14      | B5     | Blue Data Input                                                     |        |

| 15      | B4     | Blue Data Input                                                     |        |

| 16      | В3     | Blue Data Input                                                     |        |

| 17      | B2     | Blue Data Input                                                     |        |

| 18      | B1     | Blue Data Input                                                     |        |

| 19      | В0     | Blue Data Input(LSB)                                                |        |

| 20      | G7     | Green Data Input(MSB)                                               |        |

| 21      | G6     | Green Data Input                                                    |        |

| 22      | G5     | Green Data Input                                                    |        |

| 23      | G4     | Green Data Input                                                    |        |

| 24      | G3     | Green Data Input                                                    |        |

| 25      | G2     | Green Data Input                                                    |        |

| 26      | G1     | Green Data Input                                                    |        |

| 27      | G0     | Green Data Input(LSB)                                               |        |

| 28      | R7     | Red Data Input(MSB)                                                 |        |

| L       |        | I                                                                   | L      |

| 29 | R6 | Red Data Input      |  |

|----|----|---------------------|--|

| 30 | R5 | Red Data Input      |  |

| 31 | R4 | Red Data Input      |  |

| 32 | R3 | Red Data Input      |  |

| 33 | R2 | Red Data Input      |  |

| 34 | R1 | Red Data Input      |  |

| 35 | R0 | Red Data Input(LSB) |  |

| Pin No. | Symbol | Function                                                                                                                                                       | Reamrk |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 36      | GND    | Power Ground                                                                                                                                                   |        |

| 37      | DCLK   | Clock Input                                                                                                                                                    |        |

| 38      | GND    | Power Ground                                                                                                                                                   |        |

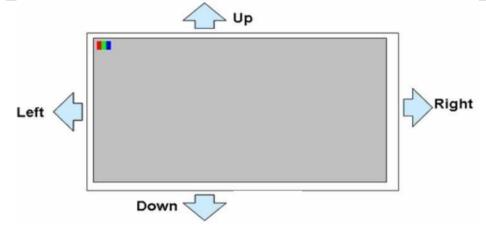

| 39      | SHLR   | Left or Right Display Control                                                                                                                                  |        |

| 40      | UPDN   | Up/Down Display Control                                                                                                                                        |        |

| 41      | VGH    | Positive Power for TFT                                                                                                                                         |        |

| 42      | VGL    | Negative Power for TFT                                                                                                                                         |        |

| 43      | AVDD   | Analog Power                                                                                                                                                   |        |

| 44      | RSTB   | Global reset pin. Active low to enter reset state. Suggest to connecting with an RC reset circuit for stability. Normally pullhigh(R=10K $\Omega$ C=1 $\mu$ F) |        |

| 45      | NC     | Not Connect                                                                                                                                                    |        |

| 46      | VCOM   | External VCOM DC input                                                                                                                                         |        |

| 47      | DITHB  | Dithering setting. DITH="H" Disable internal dithering function DITH="L" Enable internal dithering function                                                    |        |

| 48      | GND    | Power Ground                                                                                                                                                   |        |

| 49      | NC     | Not Connect                                                                                                                                                    |        |

| 50      | NC     | Not Connect                                                                                                                                                    |        |

Note 1: SHLR: left or right setting UPDN: up or down setting

| SHLR | UPDN | Data Shifting                |

|------|------|------------------------------|

| DVDD | GND  | Left Right, Up Down(Default) |

| GND  | GND  | Right Left, Up Down          |

| DVDD | DVDD | Left right, Down Up          |

| GND  | DVDD | Right Left, Down Up          |

### 5.2 Back-Light Unit

The backlight system is an edge-lighting type with 42 LED.

The characteristics of the LED are shown in the following tables.

| Item                    | Symbol | Min | Тур   | Max | Unit | Note |

|-------------------------|--------|-----|-------|-----|------|------|

| LED current             | IL     |     | 140   |     | mA   |      |

| LED voltage             | VL     | 18  | 18.6  |     | V    |      |

| Operating LED life time | Hr     |     | 20000 |     | Hour | (1)  |

Note (1) LED life time (Hr) can be defined as the time in which it continues to operate under the condition:  $Ta=25\pm3$  °C, typical IL value indicated in the above table and the fL=50k

Hz until the brightness becomes less than 50%.

40萬7

# 6.0 ELECTRICAL CHARACTERISTICS

## **6.1 TFT LCD Module**

| Item                          | Symbol | Min.  | Тур. | Max. | Unit | Note   |

|-------------------------------|--------|-------|------|------|------|--------|

| Power Supply Voltage          | VDD    | 3.0   | 3.3  | 3.6  | V    |        |

| Analog Power Supply Voltage   | AVDD   | 10.0  | 10.2 | 10.5 | V    |        |

| Gate On Power Supply Voltage  | VGH    | 7     | 20   | 35   | V    |        |

| Gate Off Power Supply Voltage | VGL    | -10.3 | -10  | -9.7 | V    |        |

| Common Power Supply Voltage   | VCOM   | 3.9   | 4.2  | 4.5  | V    | Note 1 |

| Operation frequency           | FCLK   |       |      | 200  | KHZ  |        |

Note 1: Please adjust VCOM to make the flicker level be minimum. Typ VCOM

Note (2): Be sure to apply the power Voltage as the power sequence spec.Note (3): GND=0V

# **6.2 For 1024RGB x 600 panel**

| mode                            |          |      |       |         |      |

|---------------------------------|----------|------|-------|---------|------|

| Parameter                       | 0        |      | Value | I Table |      |

| Parameter                       | Symbol   | Min. | Тур.  | Max.    | Unit |

| DCLK frequency @Frame rate=60hz | fclk     | 40.8 | 51.2  | 67.2    | Mhz  |

| Horizontal display area         | thd      |      | 1024  | Ni Ni   | DCLK |

| HSYNC period time               | th       | 1114 | 1344  | 400     | DCLK |

| HSYNC blanking                  | thb+thfp | 90   | 320   | 376     | DCLK |

| Vertical display area           | tvd      |      | (600) | 111     | Н    |

| VSYNC period time               | tv       | 610  | 635   | 800     | Н    |

| VSYNC blanking                  | tvb+tvfp | 10   | 85    | 200     | н    |

| HV mode(1)                         | 111    |        |       |      |      |

|------------------------------------|--------|--------|-------|------|------|

| HV mode<br>Horizontal input timing | OPAII) |        | RE    | 2    |      |

| Parameter                          | Symbol |        | Value |      | Unit |

| Horizontal display area            | the (  | 10     | 1024  |      | DCLK |

| DCI K francisco Fall Soft          |        | Min.   | Тур.  | Max. |      |

| DCLK frequency@ Frame kate=60hz    | fclk   | 44.9   | 51.2  | 63   | Mhz  |

| 1 Florizontal Line                 | th     | 1200   | 1344  | 1400 |      |

| Min                                | 10     | 1      |       |      | DCLK |

| HSKNO pulse width Typ.             | thpw   | thpw - |       |      |      |

| Max.                               |        |        | 140   |      | DCLK |

| HSYNC back porch                   | thbp   | 160    | 160   | 160  |      |

| HSYNC front porch                  | thfp   | 16     | 160   | 216  |      |

| ertical input timing  |        |      |      |      |      |  |

|-----------------------|--------|------|------|------|------|--|

| Value                 |        |      |      |      |      |  |

| Parameter             | Symbol | Min. | Тур. | Max. | Unit |  |

| Vertical display area | tvd    | 600  |      |      | н    |  |

| VSYNC period time     | tv     | 624  | 635  | 750  | Н    |  |

| VSYNC pulse width     | tvpw   | 1    | 2000 | 20   | н    |  |

| VSYNC back porch      | tvb    | 23   | 23   | 23   | н    |  |

| VSYNC front porch     | tvfp   | 1    | 12   | 127  | н    |  |

## **6.3** AC Electrical Characteristics

$(TA = -20 \text{ to } 85^{\circ} \text{ C}, VDD = 2.3 \text{ to } 3.6\text{V}, AVDD = 8 \text{ to } 13.5\text{V}, GND = AGND = 0\text{V})$

| Parameter              | Symbol | Condition                                                | Min. | Typ. | Max. | Unit |

|------------------------|--------|----------------------------------------------------------|------|------|------|------|

| VDD Power On Slew rate | TPOR   | From 0V to 90% VDD                                       | 59   |      | 20   | ms   |

| RSTB pulse width       | TRST   | DCLK = 65MHz                                             | 50   | 98   | -83  | us   |

| DCLK cycle time        | Tcph   | 학교의                                                      | 14   | 2    | 25   | ns   |

| DCLK pulse duty        | Towh   |                                                          | 40   | 50   | 60   | %    |

| VSD setup time         | Tvst   | -                                                        | 5/5  |      | -44  | ns   |

| VSD hold time          | Tvhd   | -                                                        | 3    | 1    | 20   | ns   |

| HSD setup time         | Thst   | -                                                        | 15   | - 15 | 2.5  | ns   |

| HSD hold time          | Thhd   | -                                                        | 5    | 92   | 2.29 | ns   |

| Data set-up time       | Tdsu   | D0[7:0], D1[7:0], D2[X:0] to DCLK                        | 5    | 100  | 1.70 | ns   |

| Data hold time         | Tdhd   | D0[7:0], D1[7:0], D2[7:0] to DCLK                        | 5    | -8   | - 63 | ns   |

| DE setup time          | Tesu   | · William                                                | 5    | - 5  | 3 29 | ns   |

| DE hold time           | Tehd   | - May " UK                                               | 5    | - E  |      | ns   |

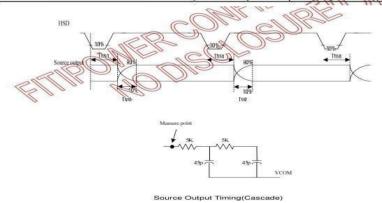

| Output stable time     | Tsst   | 10% to 90% target voltage.<br>CL 90pp R=10K ohm(Cascade) |      |      | 6    | us   |

| Output stable time     | all    | Dual gate                                                |      |      | 3    | us   |

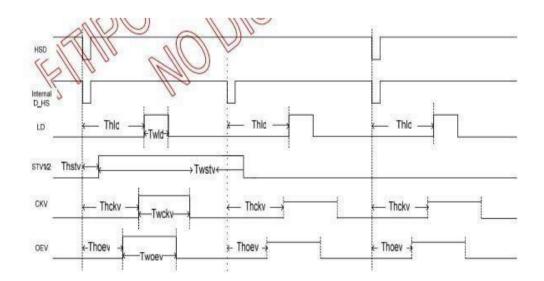

# Output Timing Table

| Parameter                      | Symbol | Min. | Тур. | Max.     | Unit | Condition     |

|--------------------------------|--------|------|------|----------|------|---------------|

| DCLK frequency                 | Fclk   | \$1  | 65   | 71       | MHz  | VDD =2.3~3.6V |

| DCLK cycle time                | Tclk   | 14.1 | 15.4 |          | ns   | 2             |

| DCLK pulse duty                | Tcwh   | 40   | 50   | 60       | %    | Tclk          |

| Time from HSD to Source Output | Thso   | - 12 | 64   |          | DCLK | 2.1/2         |

| Time from HSD to LD            | Thld   | 28   | 64   |          | DCLK | 1             |

| Time from HSD to STV           | Thstv  | 28   | 2    | <u> </u> | DCLK | 2 11 12 2     |

| Time from HSD to CKV           | Thckv  | 20   | 20   | 9        | DCLK | 11/10/10      |

| Time from HSD to OEV           | Thoev  | 20   | 4    | 5        | DOLK | 11 110        |

| LD pulse width                 | Twld   | 20   | 10   | - /      | DELK | 11 2          |

| CKV pulse width                | Twckv  | 20   | 66   | 11:      | DOLK | 3             |

| OEV pulse width                | Twoev  | 20   | 74   | (-)//    | DCLK |               |

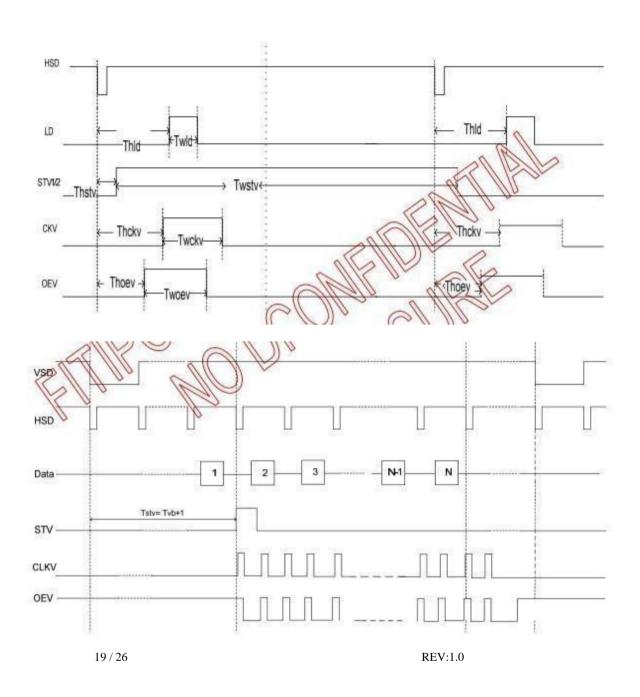

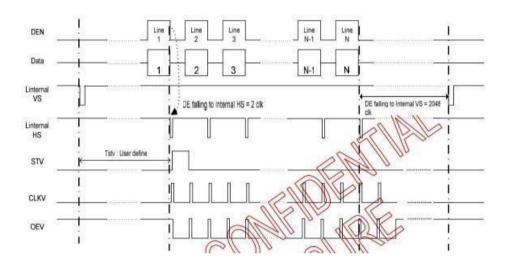

# 6.4 Timing Waveform

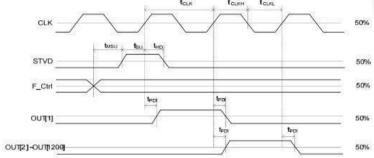

# **6.4.1 Data Input Format for TTL**

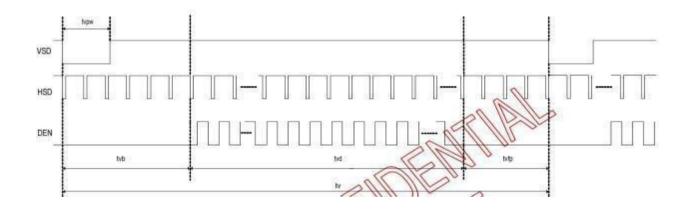

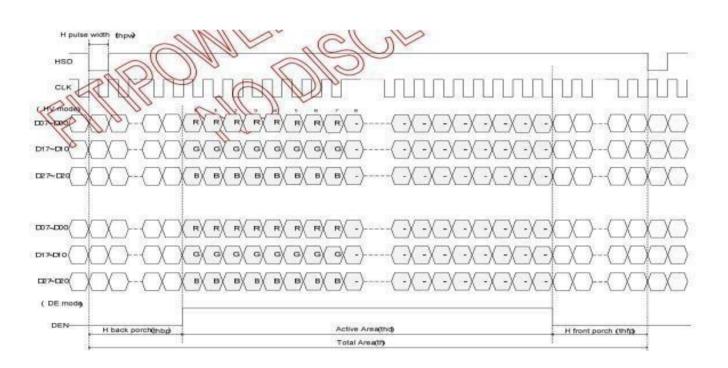

Vertical input timing

#### Horizontal input timing

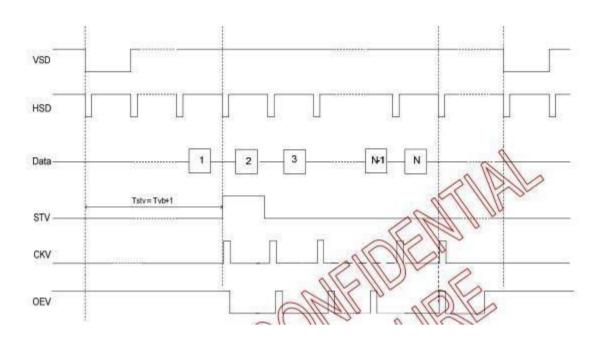

# 6.4.2 Vertical Timing Diagram HV mode(Cascade)

# **6.4.3** Vertical Timing Diagram DE mode(Cascade)

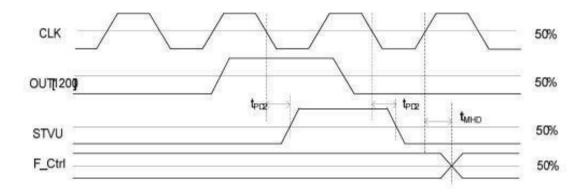

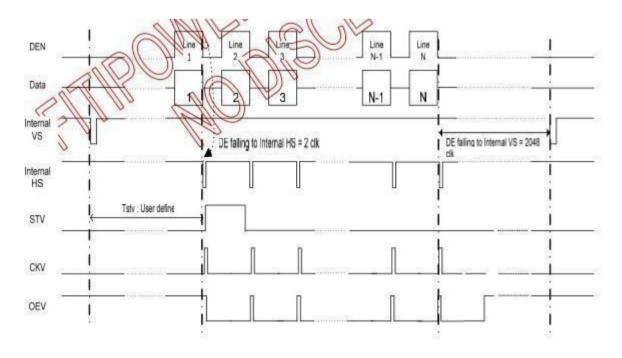

# 6.4.4Gate output

timingdiagram(Cascade)6.4.5Vertical Timing Diagram HV mode(Dual Gate)

# **6.4.6Vertical Timing Diagram DE mode(Dual Gate)**

# 6.4.7Gate output timing diagram(Dual Gate)

# 7.0 RELIABILITY TEST ITEMS

| No. | Test Item                                        | Conditions                                                                                                                                                                                                                        | Note |

|-----|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1   | High Temperature Storage                         | Ta=+80°C, 240hrs                                                                                                                                                                                                                  |      |

| 2   | Low Temperature Storage                          | Ta=-30°C, 240hrs                                                                                                                                                                                                                  |      |

| 3   | High Temperature Operation                       | Ta=+70°C, 240hrs                                                                                                                                                                                                                  |      |

| 4   | Low Temperature Operation                        | Ta=-20°C, 240hrs                                                                                                                                                                                                                  |      |

| 5   | High Temperature and High<br>Humidity(operation) | Ta=+70°C, 80%RH 240hrs                                                                                                                                                                                                            |      |

| 6   | Thermal cycling Test                             | $-30^{\circ}$ C/30 min ~ $+80^{\circ}$ C/30 min for a total 200 cycles, Start with cold temperature and end with high temperature.                                                                                                |      |

| 7   | Vibration Test<br>(Non-operation)                | <ul> <li>Frequency range:8~33.3Hz</li> <li>Stoke: 1.3 mm</li> <li>Vibration: sinusoidal wave, perpendicular axis(both x, z axis: 2hrs ,y axis: 4hrs).</li> <li>Sweep: 2.9G,33.3 Hz -400 Hz</li> <li>Cycle time: 15 min</li> </ul> |      |

| 8   | Shock Test<br>(Non-operation)                    | <ul> <li>Shock level: 980m/s 2 (equal to 100G).</li> <li>Waveform: half sinusoidal wave,6ms.</li> <li>Number of shocks: ±X,±Y,±Z axes for a total of six shock inputs.</li> </ul>                                                 |      |

| 9   | ESD Test                                         | 150pF, 330 $\Omega$ , $\pm 8kV\&\pm 15kV$ air& contact test 200pF, $0\Omega$ , $\pm 200V$ contact test                                                                                                                            | 1 2  |

|     |                                                  | 200pi, out, 200 v contact test                                                                                                                                                                                                    | _    |

Note 1: LCD glass and metal bezel

Note 2: IF connector pins

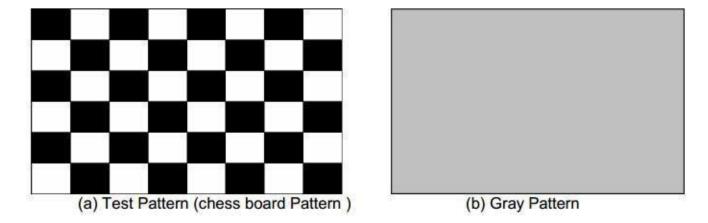

Note 3: Operation with test pattern sustained for 4hrs, then change to gray pattern immediately.

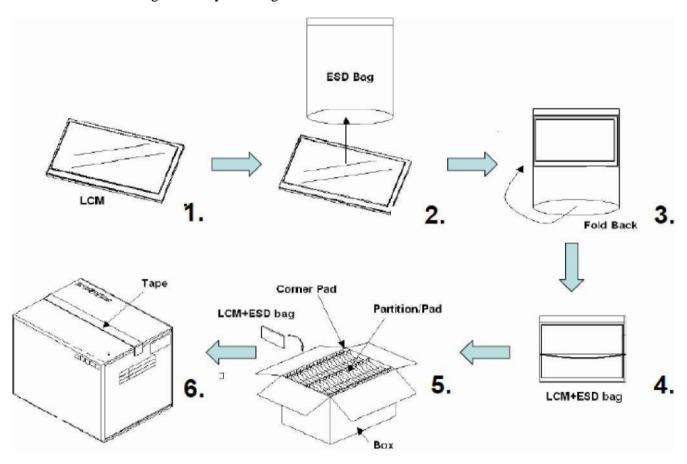

# 9.0 PACKAGE SPECIFICATION

# 10.1 Packing form

| LCM Model      | LCM Qty. in the box | Inner Box Size ( mm ) | Note |

|----------------|---------------------|-----------------------|------|

| AGO 101J0-NN-N | 60 pcs/box          | 383±5 x 373±5 x 275±5 |      |

10.2 Packing assembly drawings

| Items         | Material               | Notice   |

|---------------|------------------------|----------|

| Box           | Corrugated Paper Board | AB Flute |

| Partition/Pad | Corrugated Paper Board | B Flute  |

| Corner Pad    | Corrugated Paper Board | AB Flute |

| ESD bag       | PE                     |          |

#### 11.0 GENERAL PRECAUTION

#### 11.1 Use Restriction

This product is not authorized for use in life supporting systems, aircraft navigation control systems, military systems and any other application where performance failure could be life-threatening or otherwise catastrophic.

#### 11.2 Assembly Precaution

- 11.2.1 Please use the mounting hole on the module side in installing and do not bending or wrenching LCD in assembling. And please do not drop, bend or twist LCD module in handling.

- 11.2.2. Please design display housing in accordance with the following guide lines.

- 11.2.2.1Housing case must be destined carefully so as not to put stresses on LCD all sides and not to wrench module. The stresses may cause non-uniformity even if there is no non-uniformity statically.

- 11.2.2.2 Keep sufficient clearance between LCD module back surface and housing when the LCD module is mounted. The clearance in the design is recommended taking into account the tolerance of LCD module thickness and mounting structure height on the housing.

- 11.2.3 Please do not push or scratch LCD panel surface with any-thing hard. And do not soil LCD panel surface by touching with bare hands. (Polarizer film, surface of LCD panel is easy to be flawed.)

- 11.2.4 Please do not press any parts on the rear side such as source IC, gate IC, and FPC during handling LCD module, If pressing rear part is unavoidable, handle the LCD module with care not to damage them.

- 11.2.5 Please wipe out LCD panel surface with absorbent cotton or soft cloth in case of it being soiled.

- 11.2.6 Please wipe out drops of adhesives like saliva and water on LCD panelsurface immediately. They might damage to cause panel surface variation and color change.

- 11.2.7 Please do not take a LCD module to pieces and reconstruct it. Resolving and reconstructing modules may cause them not to work well.

#### 11.3 Disassembling or Modification

Do not disassemble or modify the module. It may damage sensitive parts inside LCD module, and may cause scratches or dust on the display. Century does not warrant the module, if customers disassemble or modify the module.

#### 11.4 Breakage of LCD Panel

- 11.4.1. If LCD panel is broken and liquid crystal spills out, do not ingest or inhale liquid crystal, and do not contact liquid crystal with skin.

- 11.4.2. If liquid crystal contacts mouth or eyes, rinse out with water immediately.

- 11.4.3. If liquid crystal contacts skin or cloths, wash it off immediately with alcohol and rinse thoroughly with water.

- 11.4.4. Handle carefully with chips of glass that may cause injury, when the glassis broken.

- 11.5 Absolute Maximum Ratings and Power Protection Circuit

- 11.5.1. Do not exceed the absolute maximum rating values, such as the supply voltage variation, input voltage variation, variation in parts' parameters, environmental temperature, etc., otherwise LCD module may be damaged.

- 11.5.2. Please do not leave LCD module in the environment of high humidity and high temperature for a long time.

- 11.5.3. It's recommended to employ protection circuit for power supply.

#### 11.6 Operation

- 11.6.1 Do not touch, push or rub the polarizer with anything harder than HB pencil lead.

- 11.6.2 Use fingerstalls of soft gloves in order to keep clean display quality, when persons handle the LCD module for incoming inspection or assembly.

- 116.3 When the surface is dusty, please wipe gently with absorbent cotton or other soft material.

- 11.6.4 Wipe off saliva or water drops as soon as possible. If saliva or water drops contact with polarizer for a long time, they may causes deformation or color fading.

- 11.6.5 When cleaning the adhesives, please use absorbent cotton wetted with alittle petroleum benzine or other adequate solvent.

#### 11.7 Static Electricity

- 11.7.1Protection film must remove very slowly from the surface of LCD moduleto prevent from electrostatic occurrence.

- 11.7.2. Because LCD module use CMOS-IC on circuit board and TFT-LCD panel, it is very weak to electrostatic discharge. Please be careful with electrostatic discharge.

- 11.7.3 Persons who handle the module should be grounded through adequate methods.

#### 11.8 Disposal

When disposing LCD module, obey the local environmental regulations.

#### 11.9 Others

- 11.9.1 A strong incident light into LCD panel might cause display characteristics' changing inferior because of Polarizer film, color filter, and other materials becoming inferior. Please do not expose LCD module direct sunlight Land Strong UV rays.

- 11.9.2 Please pay attention to a panel side of LCD module not to contact withother materials in pressing it

- 11.9.3 For the packaging box, please pay attention to the followings:

- 11.9.3.1 Packaging box and inner case for LCD are designed to protect the LCDs from the damage or scratching during transportation. Please do not open except picking LCDs up from the box.

- 11.9.3.2 Please do not pile them up more than 6 boxes(They are not designed so) And please do not turn over.

- 11.9.3.3 Please handle packaging box with care not to give them sudden shock and vibrations. And also please do not throw them up.

- 11.9.3.4 Packing box and inner case for LCDs are made of cardboard, So please pay attention not to get them wet(Such like keeping them in high humidity or wet place can occur getting them wet.)