# SPECIFICATION AGM 12864S-801

Atualizado pelo MKT em 29/04/2016

# **RECORDS OF REVISION**

| DATE       | REVISED NO. | REVISED DESCRIPTIONS | PREPARE<br>D | CHECKED | APPROVED |

|------------|-------------|----------------------|--------------|---------|----------|

| 2015-05-27 | 01          | First Issue          |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

|            |             |                      |              |         |          |

# **CONTENTS**

| 1. | GENERAL SPECIFICATIONS                   | 4    |

|----|------------------------------------------|------|

| 2. | BLOCK DIAGRAM                            | 5    |

| 3. | OUTLINE DRAWING                          | 6    |

| 4. | INTERFACE ASSIGNMENT                     | 9    |

| 5. | APPLICATION CIRCUIT                      | 9    |

| 6. | TIMING CHARACTERISTICS                   | 10   |

| 7. | POWER ON/OFF SEQUENCE                    | 14   |

| 8. | RECOMMENDED INITIAL CODES                | 16   |

| 9. | INSTRUCTION TABLE                        | .17  |

| 10 | ABSOLUTE MAXIMUM RATING                  | 17   |

| 11 | ELECTRICAL CHARACTERISTICS               | 18   |

| 12 | . LED BACKLIGHT                          | 18   |

| 13 | . POTICAL CHARACTERISTICS                | 19   |

| 14 | . ENVIRONMENTAL ABSOLUTE MAXIMUM RATINGS | 22   |

| 15 | . RELIABILITY TEST                       | 22   |

| 16 | . STANDARD OF INSPECTION                 | 24   |

| 17 | . USING LCD MODULES                      | . 28 |

# **1. GENERAL SPECIFICATIONS**

# 1-1.DESCRIPTION:

The AGM 12864S-801 is a dot matrix mono Liquid Crystal Display Module(LCM). This specification covers the delivery requirements for the liquid crystal display delivered by AGTECHNOLOGIES to Customer.

# 1-2. FEATURES

- (1) Display Type: STN, Negative Blue, Transmissive, 6 O'clock

- (2) Driving Method: 1/65 duty, 1/9 bias

- (3) Built-in controller: ST7565R

- (4) With White Backlight

| ITEM               | SPECIFICATIONS         | UNIT |

|--------------------|------------------------|------|

| DISP.CONSTRUCTION  | 128*64 Dots            |      |

| OUTLINE DIMEMSIONS | 77.4(W)*52.4(H)*6.5(T) | mm   |

| VIEWING AREA       | 70.0(W) *40.0(H)       | mm   |

| ACTIVE AREA        | 66.53(W) * 33.25(H)    | mm   |

| DOT SIZE           | 0.49(W) * 0.49(H)      | mm   |

| DOT PITCH          | 0.52(W) x 0.52(H)      | mm   |

| ASSY.TYPE          | COG+FPC+BL             |      |

| INTERFACE          | 6800 ,8080,SPI         |      |

# **1-3.GENERAL SPECIFICATION**

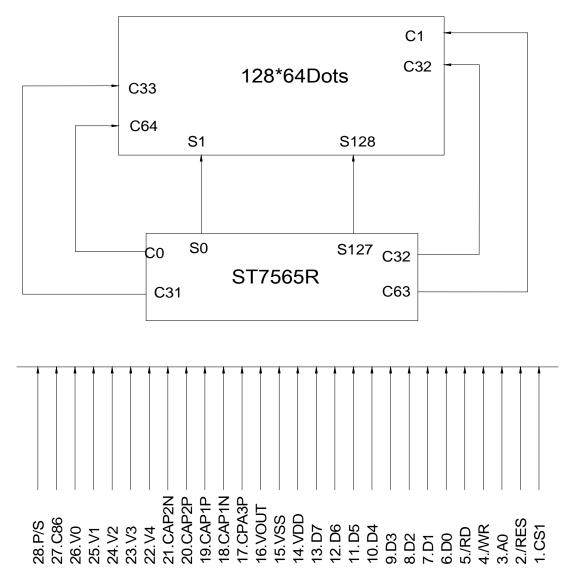

# 2. BLOCK DIAGRAM

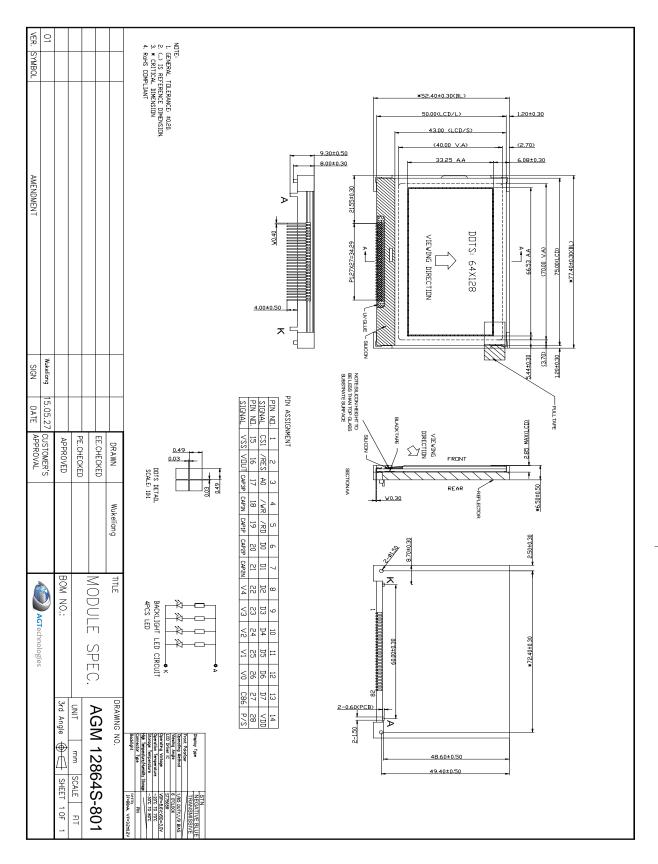

# 3. OUTLINE DRAWING

# 4. INTERFACE ASSIGNMENT

| PIN NO. |                                                                                                                | SYMBOL                                                                                                                                                                                                           |                         |                                                                                                                                                                                                                                                                                          |      |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| 1       | Chip Select. Chip is selected when CS0 = "L". When the chip is not selected, D[7:0] will be of high impedance. |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          |      |  |  |  |

| 2       |                                                                                                                | zed by settir<br>operation is                                                                                                                                                                                    | •                       | to LOW.<br>ned at the RES signal level.                                                                                                                                                                                                                                                  | /RES |  |  |  |

| 3       | discrim<br>A0=HI                                                                                               | Normally the lowest order bit of the MPU address bus is connected to<br>discriminate data / commands.<br>A0=HIGH: Indicates that D0 to D7 are display data.<br>A0=LOW: Indicates that D0 to D7 are control data. |                         |                                                                                                                                                                                                                                                                                          |      |  |  |  |

|         | Read/V                                                                                                         | Vrite executio                                                                                                                                                                                                   | n control               | pin. When PSB is "H",                                                                                                                                                                                                                                                                    |      |  |  |  |

|         | C86                                                                                                            | MPU Type                                                                                                                                                                                                         | RWR                     | Description                                                                                                                                                                                                                                                                              |      |  |  |  |

| 4       | н                                                                                                              | 6800<br>series                                                                                                                                                                                                   | R/W                     | Read/Write control input pin.<br>R/W="H": read.<br>R/W="L": write.                                                                                                                                                                                                                       | /WR  |  |  |  |

|         | L                                                                                                              | 8080<br>series                                                                                                                                                                                                   | /WR                     | Write enable input pin.<br>Signals on D[7:0] will be latched at the rising<br>edge of /WR signal.                                                                                                                                                                                        |      |  |  |  |

|         | RWR is                                                                                                         | s not used in s                                                                                                                                                                                                  | erial inte              | rface and should be fixed to "H" by VDD.                                                                                                                                                                                                                                                 |      |  |  |  |

|         | Read/V                                                                                                         |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          |      |  |  |  |

|         | C86                                                                                                            | MPU Type                                                                                                                                                                                                         | ERD                     | Description                                                                                                                                                                                                                                                                              |      |  |  |  |

| 5       | H<br>L<br>ERD is                                                                                               | 68þ0<br>series<br>8080<br>series<br>not used in se                                                                                                                                                               | E<br>/RD<br>erial inter | Read/Write control input pin.<br>R/W="H": When E is "H", D[7:0] are in output<br>mode.<br>R/W="L": Signals on D[7:0] are latched at the<br>falling edge of E signal.<br>Read enable input pin.<br>When /RD is "L", D[7:0] are in output mode.<br>face and should be fixed to "H" by VDD. | RD   |  |  |  |

| 6       |                                                                                                                |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D0   |  |  |  |

| 7       | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D1   |  |  |  |

| 8       | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D2   |  |  |  |

| 9       | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D3   |  |  |  |

| 10      | Data bı                                                                                                        | 15                                                                                                                                                                                                               |                         |                                                                                                                                                                                                                                                                                          | D4   |  |  |  |

| 11      | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D5   |  |  |  |

| 12      | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D6   |  |  |  |

| 13      | 1                                                                                                              |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | D7   |  |  |  |

| 14      | Comm                                                                                                           | only used w                                                                                                                                                                                                      | ith the                 | MPU power supply pin Vcc.                                                                                                                                                                                                                                                                | VDD  |  |  |  |

| 15      | GND                                                                                                            | -                                                                                                                                                                                                                |                         |                                                                                                                                                                                                                                                                                          | VSS  |  |  |  |

| 16      | NC                                                                                                             |                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                                                          | VOUT |  |  |  |

# **8**/30

| 17 |                               |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

|----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|--|

| 18 | DC-DC voltage                 | C-DC voltage converter for LCD driver circuit. If using built-in voltage booster                                                                               |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 19 | circuit, the appli            | circuit, the application circuit please refers to section of Liquid Crystal Driver<br>Power Circuit.                                                           |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 20 | Power Circuit.                |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 21 |                               |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 22 |                               |                                                                                                                                                                |                                                                                                                                  | V4   |  |  |  |  |  |  |  |  |  |

| 23 | The power supp                | The power supply pins for LCD.<br>Insure the voltage levels of VOUT, V0, V1, V2, V3 and V4 always match below<br>relation: VOUT > V0 > V1 > V2 > V3 > V4 > VSS |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 24 |                               |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 25 | relation: VOUT                |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 26 |                               |                                                                                                                                                                |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 27 | C86 selects the<br>PSB<br>"H" | e micropro<br>C86<br>"H"                                                                                                                                       | cessor type in parallel interface mode. Selected Interface Parallel 6800 Series MPU Interface Parallel 9090 Series MPU Interface | C86  |  |  |  |  |  |  |  |  |  |

| 27 | н<br>"L"                      | "X"                                                                                                                                                            | Parallel 8080 Series MPU Interface<br>Serial 4-Line SPI Interface                                                                | 0.80 |  |  |  |  |  |  |  |  |  |

|    | Please refer t                | Please refer to "APPLICATION NOTES" and "Microprocessor Interface"<br>(Section 6) for detailed connection of the selected interface.                           |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

| 28 | PSB selects the               | PSB selects the interface type: Serial or Parallel.                                                                                                            |                                                                                                                                  |      |  |  |  |  |  |  |  |  |  |

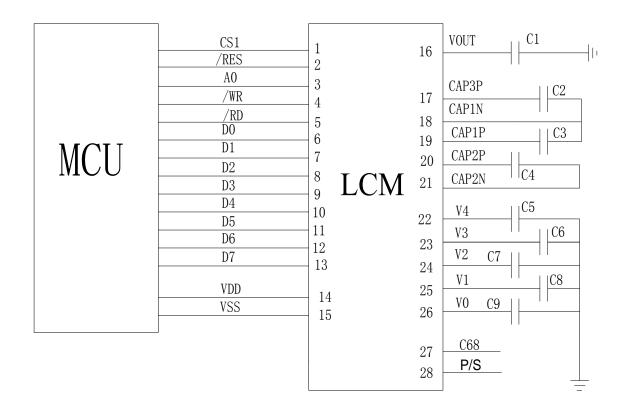

# 5. APPLICATION CIRCUIT

C1~C9: 1.0uF/25V

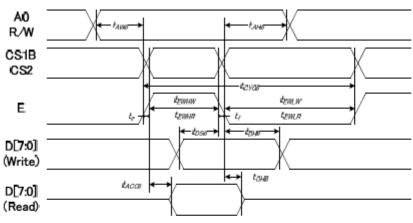

# 6. TIMING CHARACTERISTICS

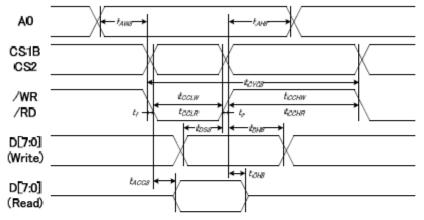

System Bus Timing for 6800 Series MPU

(VDD = 3.3V , Ta = 25°C)

| ltem                          | Signal | Symbol | Condition   | Min. | Max. | Unit |

|-------------------------------|--------|--------|-------------|------|------|------|

| Address setup time            | 4.0    | tAW6   |             | 0    | _    |      |

| Address hold time             | A0     | tAH6   |             | 0    | —    | ]    |

| System cycle time             |        | tCYC6  |             | 240  | _    | 1    |

| Enable L pulse width (WRITE)  | 1      | tEWLW  |             | 80   | —    | 1    |

| Enable H pulse width (WRITE)  | E      | tEWHW  |             | 80   | _    | ]    |

| Enable L pulse width (READ)   | 1      | tEWLR  |             | 80   | _    | ns   |

| Enable H pulse width (READ)   |        | tEWHR  |             | 140  |      | ]    |

| Write data setup time         |        | tDS6   |             | 40   | _    | ]    |

| Write data hold time          | D(7:01 | tDH6   |             | 10   | _    | 1    |

| Read data access time         | D[7:0] | tACC6  | CL = 100 pF | —    | 70   | ]    |

| Read data output disable time | ]      | tOH6   | CL = 100 pF | 5    | 50   |      |

# **11**/30

| = 2.7V |  |

|--------|--|

|        |  |

|        |  |

|        |  |

|        |  |

| Item                          | Signal | Symbol | Condition   | Min. | Max. | Unit |

|-------------------------------|--------|--------|-------------|------|------|------|

| Address setup time            | AO     | tAW6   |             | 0    | _    |      |

| Address hold time             | AU     | tAH6   |             | 0    | _    |      |

| System cycle time             |        | tCYC6  |             | 400  | -    | ]    |

| Enable L pulse width (WRITE)  |        | tEWLW  |             | 220  | _    | ]    |

| Enable H pulse width (WRITE)  | E      | tEWHW  |             | 180  | _    |      |

| Enable L pulse width (READ)   |        | tEWLR  |             | 220  | —    | ns   |

| Enable H pulse width (READ)   |        | tEWHR  |             | 180  | _    |      |

| Write data setup time         |        | tDS6   |             | 40   | _    |      |

| Write data hold time          | D(7:0) | tDH6   |             | 0    | —    | 1    |

| Read data access time         | D[7:0] | tACC6  | CL = 100 pF | —    | 140  | ]    |

| Read data output disable time |        | tOH6   | CL = 100 pF | 10   | 100  |      |

\*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,

(tr + tf) ≤ (tCYC6 - tEWLW - tEWHW) for (tr + tf) ≤ (tCYC6 - tEWLR - tEWHR) are specified.

\*2 All timing is specified using 20% and 80% of VDD as the reference.

\*3 tEWLW and tEWLR are specified as the overlap between CS1B being "L" (CS2="H") and E.

## System Bus Timing for 8080 Series MPU

(VDD = 3.3V , Ta = 25 C)

| Item                      | Signal | Symbol | Condition   | Min. | Max. | Unit |

|---------------------------|--------|--------|-------------|------|------|------|

| Address setup time        | 40     | tAW8   |             | 0    | _    |      |

| Address hold time         | A0     | tAH8   |             | 0    | _    |      |

| System cycle time         |        | tCYC8  |             | 240  | _    | ]    |

| /WR L pulse width (WRITE) | /WR    | tCCLW  |             | 80   | —    | 1    |

| /WR H pulse width (WRITE) |        | tCCHW  |             | 80   | —    | ]    |

| /RD L pulse width (READ)  | RD     | tCCLR  |             | 140  | _    | ns   |

| /RD H pulse width (READ)  | RD     | tCCHR  |             | 80   |      |      |

| WRITE Data setup time     |        | tDS8   |             | 40   | _    | ]    |

| WRITE Data hold time      | D(7:01 | tDH8   |             | 20   | _    | ]    |

| READ access time          | D[7:0] | tACC8  | CL = 100 pF | —    | 70   |      |

| READ Output disable time  |        | tOH8   | CL = 100 pF | 5    | 50   |      |

# **12**/30

| $-2 \times 2$ | $T_{2} \rightarrow 2E(0)$ |

|---------------|---------------------------|

| = 2 / 2       | 12 = 22 1 1               |

|               | , ia -20 0)               |

|               | = 2.7V                    |

| Item                      | Signal | Symbol | Condition   | Min. | Max. | Unit |

|---------------------------|--------|--------|-------------|------|------|------|

| Address setup time        | AO     | tAW8   |             | 0    | _    |      |

| Address hold time         | AU     | tAH8   |             | 0    | _    | ]    |

| System cycle time         |        | tCYC8  |             | 400  | _    | 1    |

| /WR L pulse width (WRITE) | /WR    | tCCLW  |             | 220  | _    | ]    |

| /WR H pulse width (WRITE) |        | tCCHW  |             | 180  | _    | 1    |

| /RD L pulse width (READ)  | DD     | tCCLR  |             | 220  | _    | ns   |

| /RD H pulse width (READ)  | RD     | tCCHR  |             | 180  | _    | 1    |

| WRITE Data setup time     |        | tDS8   |             | 40   | _    | 1    |

| WRITE Data hold time      | D(7:0) | tDH8   |             | 0    | _    | 1    |

| READ access time          | D[7:0] | tACC8  | CL = 100 pF | _    | 140  | 1    |

| READ Output disable time  |        | tOH8   | CL = 100 pF | 10   | 100  |      |

\*1 The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,

(tr + tf)  $\,\leq\,$  (tCYC8  $\,$  - tCCLW  $\,$  - tCCHW) for (tr + tf)  $\,\leq\,$  (tCYC8  $\,$  - tCCLR  $\,$  - tCCHR) are specified.

\*2 All timing is specified using 20% and 80% of VDD as the reference.

\*3 tCCLW and tCCLR are specified as the overlap between CS1B being "L" (CS2="H") and WR and RD being at the "L" level.

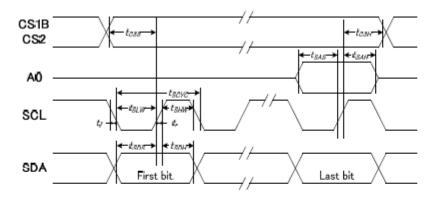

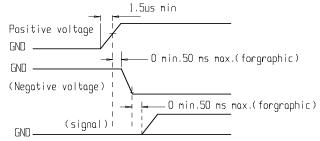

# System Bus Timing for 4-Line Serial Interface

(VDD = 3.3V , Ta = 25 C)

| Item                 | Signal | Symbol | Condition | Min. | Max. | Unit |

|----------------------|--------|--------|-----------|------|------|------|

| Serial clock period  |        | tSCYC  |           | 50   | —    |      |

| SCLK "H" pulse width | SCLK   | tSHW   |           | 25   | _    |      |

| SCLK "L" pulse width |        | tSLW   |           | 25   | _    | 1    |

| Address setup time   | A0     | tSAS   |           | 20   | —    | 1    |

| Address hold time    | AU     | tSAH   |           | 10   | —    | ns   |

| Data setup time      | SDA    | tSDS   |           | 20   | _    |      |

| Data hold time       | SDA    | tSDH   |           | 10   | —    | ]    |

| CS-SCLK time         | CS1B   | tCSS   |           | 20   | _    | ]    |

| CS-SCLK time         | CS2    | tCSH   |           | 40   | _    | ]    |

(VDD = 2.7V , Ta = 25 C)

| Item                 | Signal | Symbol | Condition | Min. | Max. | Unit |

|----------------------|--------|--------|-----------|------|------|------|

| Serial clock period  |        | tSCYC  |           | 100  | _    |      |

| SCLK "H" pulse width | SCLK   | tSHW   |           | 50   | —    |      |

| SCLK "L" pulse width |        | tSLW   |           | 50   | _    |      |

| Address setup time   | 4.0    | tSAS   |           | 30   | _    |      |

| Address hold time    | AO     | tSAH   |           | 20   | —    | ns   |

| Data setup time      | 204    | tSDS   |           | 30   | —    |      |

| Data hold time       | SDA    | tSDH   |           | 20   | _    |      |

| CS-SCLK time         | CS1B   | tCSS   |           | 30   | —    |      |

| CS-SCLK time         | CS2    | tCSH   |           | 60   | _    |      |

\*1 The input signal rise and fall time (tr, tf) are specified at 15 ns or less.

\*2 All timing is specified using 20% and 80% of VDD as the standard.

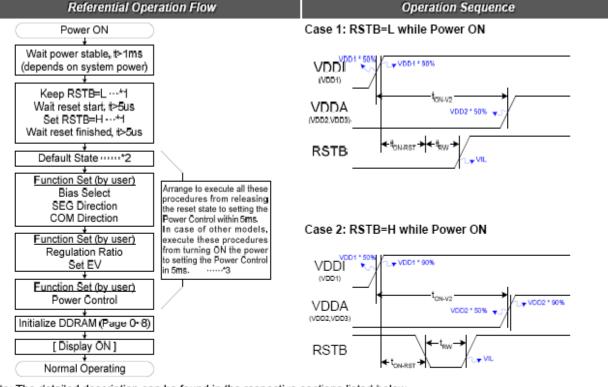

# 7. POWER ON/OFF SEQUENCE

# 7-1. POWER ON SEQUENCE

#### Power ON

Note: The detailed description can be found in the respective sections listed below.

- 1. Please refer to the timing specification of  $t_{RW}$  and  $t_{R}$ .

- Refer to Section RESET CIRCUIT.

- The 5ms requirement depends on the characteristics of LCD panel and the external component of the power circuit. It is recommended to check with the real products with external component.

- 4. The detailed instruction functionality is described in Section INSTRUCTION DESCRIPTION;

- 5. Power stable is defined as the time that the later power (VDDI or VDDA) reaches 90% of its rated voltage.

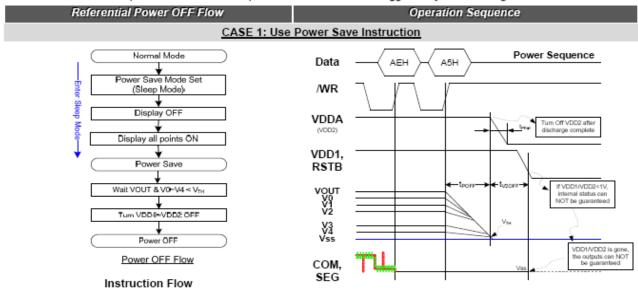

## 7-2. POWER OFF SEQUENCE

#### Power OFF Flow and Sequence

In power save mode, LCD outputs are fixed to VSS and all analog outputs are discharged. The power can be turned OFF after ST7565R is in the power save mode. The power save mode can be triggered by the following two methods.

After the built-in power circuits are OFF and completely discharged (the power level of built-in analog circuit is smaller than  $V_{TH}$  of LCD panel), the power (VDDI, VDDA) can be removed.  $V_{TH}$  is around 0.2V to 1.0V.

Normal Mode

Set RSTB=L (wait > t<sub>RM</sub>)

Set RSTB-H

Wait 260m s

Turn VDD1~VDD2 OFF

Power OFF

Power OFF Flow

Instruction Flow

After the built-in power circuits are OFF and completely discharged (the power level of built-in analog circuit is smaller than  $V_{TH}$  of LCD panel), the power (VDDI, VDDA) can be removed.  $V_{TH}$  is around 0.2V to 1.0V.

Note:

- t<sub>POFF</sub>: Internal Power discharge time. Discharge time for built-in circuit is dependent on user's system design.

- t<sub>V2OFF</sub>: Period between VDDI and VDDA OFF time. => 0 ms (min).

- It is NOT recommended to turn VDDI OFF before VDDA. Without VDDI, the internal status cannot be guaranteed and internal discharge-process maybe stopped. The un-discharged power maybe flows into COM/SEG output(s) and the liquid crystal in panel maybe polarized.

- 4. IC will NOT be damaged if either VDDI or VDDA is OFF while another is ON.

- 5. The timing is dependent on panel loading and the external capacitor(s).

# 8. RECOMMENDED INITIAL CODES

void Initial(void)

{

}

| writec(0xa2);                                                                                    | /* 1/9 bias */                                                                                                                   |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| writec(0xe2);                                                                                    |                                                                                                                                  |

| writec(0xa0);                                                                                    | /* ADC select , Normal */                                                                                                        |

| writec(0xc8);                                                                                    | /* Common output reverse */                                                                                                      |

| writec(0xa6);                                                                                    | /* normal display 1=on */                                                                                                        |

| writec(0x2c);                                                                                    |                                                                                                                                  |

| writec(0x2e);                                                                                    |                                                                                                                                  |

| writec(0x2f);                                                                                    | /* V/C off, V/R off, V/F on */                                                                                                   |

|                                                                                                  |                                                                                                                                  |

|                                                                                                  |                                                                                                                                  |

| writec(0xf8);                                                                                    | /***5 booster***/                                                                                                                |

| writec(0xf8);<br>writec(0x00);                                                                   | /***5 booster***/                                                                                                                |

|                                                                                                  | /***5 booster***/<br>/* internal resistor ratio */                                                                               |

| writec(0x00);                                                                                    |                                                                                                                                  |

| <pre>writec(0x00);<br/>writec(0x25);</pre>                                                       | /* internal resistor ratio */                                                                                                    |

| <pre>writec(0x00);<br/>writec(0x25);<br/>writec(0x81);</pre>                                     | <pre>/* internal resistor ratio */ /* electronic volume mode set */</pre>                                                        |

| <pre>writec(0x00);<br/>writec(0x25);<br/>writec(0x81);<br/>writec(0x16);</pre>                   | <pre>/* internal resistor ratio */ /* electronic volume mode set */ /* electronic volume */</pre>                                |

| <pre>writec(0x00);<br/>writec(0x25);<br/>writec(0x81);<br/>writec(0x16);<br/>writec(0x40);</pre> | <pre>/* internal resistor ratio */ /* electronic volume mode set */ /* electronic volume */ /* display start first line */</pre> |

**16**/30

# 9. INSTRUCTION TABLE

|                      |    | R/W   |      |    | С   | OMMA   | ND BYT | BYTE |     |     |                                                                                  |

|----------------------|----|-------|------|----|-----|--------|--------|------|-----|-----|----------------------------------------------------------------------------------|

| INSTRUCTION          | A0 | (RWR) | D7   | D6 | D5  | D4     | D3     | D2   | D1  | D0  | DESCRIPTION                                                                      |

| Display ON/OFF       | 0  | 0     | 1    | 0  | 1   | 0      | 1      | 1    | 1   | D   | D=1, display ON<br>D=0, display OFF                                              |

| Set Start Line       | 0  | 0     | 0    | 1  | S5  | S4     | S3     | S2   | S1  | SO  | Set display start line                                                           |

| Set Page Address     | 0  | 0     | 1    | 0  | 1   | 1      | Y3     | Y2   | Y1  | YO  | Set page address                                                                 |

| Set Column Address   | 0  | 0     | 0    | 0  | 0   | 1      | X7     | X6   | X5  | X4  | Set column address (MSB)                                                         |

| Set Column Address   | 0  | 0     | 0    | 0  | 0   | 0      | Х3     | X2   | X1  | XO  | Set column address (LSB)                                                         |

| Read Status          | 0  | 1     | BUSY | MX | D   | RST    | 0      | 0    | 0   | 0   | Read IC Status                                                                   |

| Write Data           | 1  | 0     | D7   | D6 | D5  | D4     | D3     | D2   | D1  | D0  | Write display data to RAM                                                        |

| Read Data            | 1  | 1     | D7   | D6 | D5  | D4     | D3     | D2   | D1  | D0  | Read display data from RAM                                                       |

| SEG Direction        | 0  | 0     | 1    | 0  | 1   | 0      | 0      | 0    | 0   | MX  | Set scan direction of SEG<br>MX=1, reverse direction<br>MX=0, normal direction   |

| Inverse Display      | 0  | 0     | 1    | 0  | 1   | 0      | 0      | 1    | 1   | INV | INV =1, inverse display<br>INV =0, normal display                                |

| All Pixel ON         | 0  | 0     | 1    | 0  | 1   | 0      | 0      | 1    | 0   | AP  | AP=1, set all pixel ON<br>AP=0, normal display                                   |

| Bias Select          | 0  | 0     | 1    | 0  | 1   | 0      | 0      | 0    | 1   | BS  | Select bias setting<br>0=1/9; 1=1/7 (at 1/65 duty)                               |

| Read-modify-Write    | 0  | 0     | 1    | 1  | 1   | 0      | 0      | 0    | 0   | 0   | Column address increment:<br>Read:+0 , Write:+1                                  |

| END                  | 0  | 0     | 1    | 1  | 1   | 0      | 1      | 1    | 1   | 0   | Exit Read-modify-Write mode                                                      |

| RESET                | 0  | 0     | 1    | 1  | 1   | 0      | 0      | 0    | 1   | 0   | Software reset                                                                   |

| COM Direction        | 0  | O     | 1    | 1  | 0   | 0      | MY     | -    |     | -   | Set output direction of COM<br>MY=1, reverse direction<br>MY=0, normal direction |

| Power Control        | 0  | 0     | 0    | 0  | 1   | 0      | 1      | VB   | VR  | VF  | Control built-in power circuit<br>ON/OFF                                         |

| Regulation Ratio     | 0  | 0     | 0    | 0  | 1   | 0      | 0      | RR2  | RR1 | RR0 | Select regulation resistor ratio                                                 |

| Set EV               | 0  | 0     | 1    | 0  | 0   | 0      | 0      | 0    | 0   | 1   | Double command!! Set                                                             |

| Selev                | 0  | 0     | 0    | 0  | EV5 | EV4    | EV3    | EV2  | EV1 | EV0 | electronic volume (EV) level                                                     |

| Power Save Mode Set  | 0  | 0     | 1    | 0  | 1   | 0      | 1      | 1    | 0   | MD  | MD=0, sleep mode                                                                 |

| r ower save mode set | 0  | 0     | 0    | 0  | 0   | 0      | 0      | 0    | 0   | 0   | MD=1, normal                                                                     |

| Power Save           | 0  | 0     |      |    | Co  | mpound | Comm   | and  |     |     | Display OFF + All Pixel ON                                                       |

|                      | 0  | 0     | 1    | 1  | 1   | 1      | 1      | 0    | 0   | 0   | Double command!!<br>Set booster level:                                           |

| Set Booster          | 0  | 0     | 0    | 0  | 0   | 0      | 0      | 0    | BL1 | BL0 | BL[1:0]=(0,0), x2, x3, x4<br>BL[1:0]=(0,1), x5<br>BL[1:0]=(1,1), x6              |

| NOP                  | 0  | 0     | 1    | 1  | 1   | 0      | 0      | 0    | 1   | 1   | No operation                                                                     |

| Test                 | 0  | 0     | 1    | 1  | 1   | 1      | -      | -    | -   | -   | Do NOT use.<br>Reserved for testing.                                             |

Note: Symbol "-" means this bit can be "H" or "L".

# 10. ABSOLUTE MAXIMUM RATING

| ITEM                     | SVMDOI             | STA  | UNIT |      |    |

|--------------------------|--------------------|------|------|------|----|

|                          | SYMBOL MIN TYP MAX |      | UNII |      |    |

| SUPPLY VOLTAGE FOR LOGIC | VDD-VSS            | -0.3 | -    | 3.6  | V  |

| LCD POWER SUPPLY VOLTAGE | VIN                | -0.3 | -    | 13.5 | V  |

| OPERATING TEMPERATURE    | T <sub>OP</sub>    | -20  | -    | 70   | °C |

| STORAGE TEMPERATURE      | T <sub>STG</sub>   | -30  | -    | 80   | °C |

# II. ELECTRICAL CHARACTERISTICS ITEM SYMBOL

| ITEM                     | SYMBOL  | CONDITIONS | STANE  | UNIT |        |      |

|--------------------------|---------|------------|--------|------|--------|------|

|                          | SIMBOL  | CONDITIONS | MIN    | ТҮР  | MAX    | UNII |

| SUPPLY VOLTAGE FOR LOGIC | VDD-VSS |            | 2.7    | 3.0  | 3.3    | V    |

| SUPPLY VOLTAGE FOR LCD   | V0–VSS  |            | 8.4    | 8.6  | 8.8    | V    |

| INPUT VOLTAGE "H" LEVEL  | VIH     | Ta= +25°⊖  | 0.8VDD | -    | VDD    | V    |

| INPUT VOLTAGE "L" LEVEL  | VIL     | Ta=+25°C   | VSS    | -    | 0.2VDD | V    |

| OUTPUT VOLTAGE "H" LEVEL | VOH     |            | 0.8VDD | -    | VDD    | V    |

| OUTPUT VOLTAGE "L" LEVEL | VOL     |            | VSS    | -    | 0.2VDD | V    |

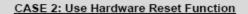

# 12. LED BACKLIGHT

12-1 LED CIRCUIT:

12-2.ABSOLUTE MAXIMUN RATING

| PARAMETER             | SYMBOL | SPECIFICATIONS | UNIT |

|-----------------------|--------|----------------|------|

| POWER DISSIPATION     | PD     | 272            | mW   |

| FORWARD CURRENT       | Ifm    | 80             | mA   |

| FORWARD VOLTAGE       | Vf     | 3.2            | V    |

| REVERSE VOLTAGE       | Vr     | 5              | V    |

| OPERATION TEMPERATURE | TOPR   | -20 ~+70       | °C   |

| STORAGE TEMPERATURE   | TSTG   | -30 ~+80       | °C   |

# 12-3. ELECTRICAL CHARACTERISTICS (Ta=25°C)

| PARAMETER                 | SYMBOL         | LIGHT  | CONDITIONS | STANDARD<br>VALUE |      |      | UNIT              |

|---------------------------|----------------|--------|------------|-------------------|------|------|-------------------|

|                           |                | SOURCE |            | MIN               | ТҮР  | MAX  |                   |

| FORWARD VOLTAGE           | Vf             |        | If=80mA    | 3.0               | 3.2  | 3.4  | V                 |

| REVERSE CURRENT           | IR             |        | Vr=5V      |                   |      | 10   | uA                |

| SURFACE BRIGHTNESS        | Lv             | WHITE  | If=80mA    |                   | 1100 |      | cd/m <sup>2</sup> |

| LUMINOUS UNIFORMITY       | Δ              | WHILE  | If=80mA    | 70%               |      |      |                   |

| Color chromaticiy (White) | W <sub>x</sub> |        | If=80mA    | 0.26              | 0.28 | 0.30 |                   |

|                           | $W_y$          |        | If=80mA    | 0.27              | 0.29 | 0.31 |                   |

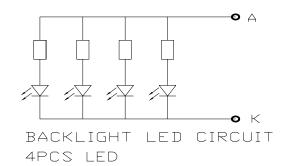

# **13. OPTICAL CHARACTERISTICS**

| Ite     | em               | Symbol  | Temp.         | Condition                   | Min.                | Тур.  | Max.                 | Unit. | Note |      |      |   |

|---------|------------------|---------|---------------|-----------------------------|---------------------|-------|----------------------|-------|------|------|------|---|

|         | D.               |         |               |                             |                     | -20°C |                      |       | 2100 | 2500 |      |   |

|         | Rise<br>time     | tr      | 25℃           |                             |                     | 120   | 150                  |       |      |      |      |   |

| Respon  | tille            |         | 70            | $\theta = 0^{\circ}$        |                     | 38    | 45                   | mS    |      |      |      |   |

| se Time | 6.11             |         | <b>-20°</b> ℃ | φ=0°                        |                     | 4400  | 5300                 | 1115  | -    |      |      |   |

|         | fall<br>time     | time tf | 25℃           |                             |                     | 200   | 250                  |       |      |      |      |   |

|         | time             |         | 70            |                             |                     | 65    | 80                   |       |      |      |      |   |

|         |                  |         |               | $\Phi = 0^{\circ}$          |                     | 25    | 30                   |       |      |      |      |   |

| Viewin  | Angla            | le θ    | Angle θ       | 25℃                         | $\Phi = 90^{\circ}$ |       | 30                   | 40    | dag  |      |      |   |

| viewing | , Angle $\theta$ |         |               | θ                           | θ                   | Cr≥2  | $\Phi = 180^{\circ}$ |       | 25   | 30   | deg. | - |

|         |                  |         |               | Φ=270°                      |                     | 25    | 30                   |       |      |      |      |   |

| Contras | st Ratio         | K       | 25℃           | $\theta = \phi = 0^{\circ}$ |                     | 3     | 4                    | -     | -    |      |      |   |

#### (1) DEFINITION OF VIEWING ANGLE

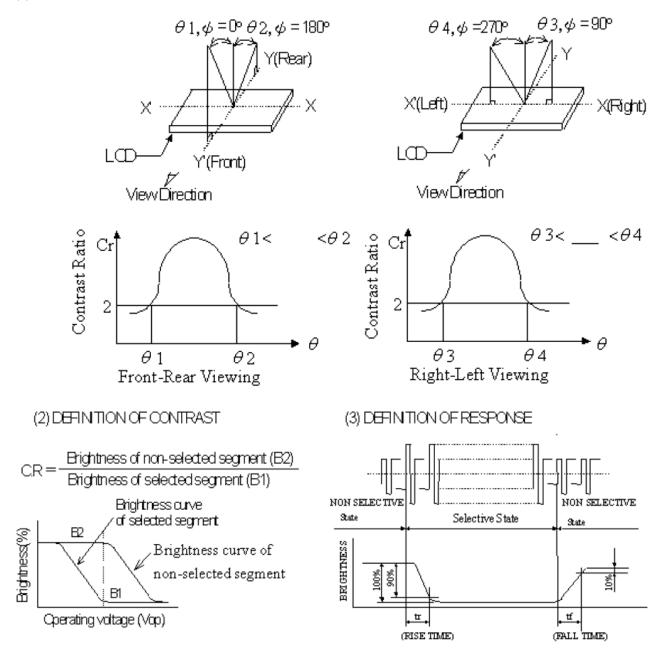

(4) MEASURING INSTRUMENTS FOR ELECTRO-OPTICAL CHARACTERISTICS

21/30

\*1.Light source position for measuring the reflective type of LCD panel\*2.Light source position for measuring the transflective / transmissive types of LCD panel

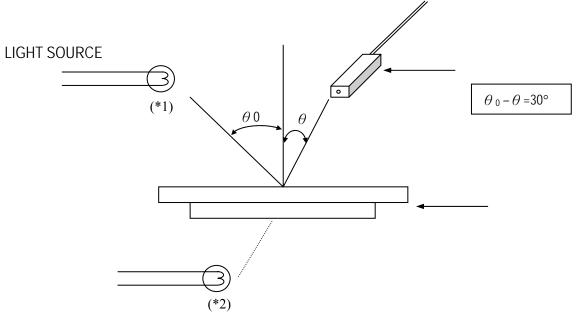

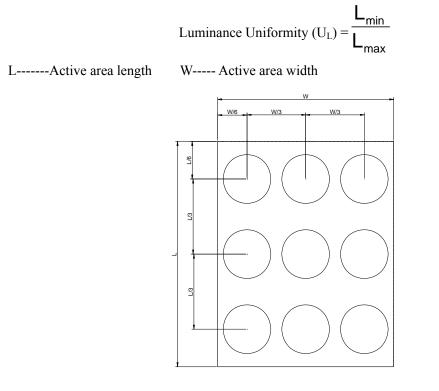

# (5) DEFINITION OF LUMINANCE UNIFORMITY

To test for uniformity, the tested area is divided into 3 rows and 3 columns. The measurement spot is placed at the center of each circle as below.

Fig .Definition of luminance uniformity

$\boldsymbol{L}_{min}$  : The measured minimum luminance of all measurement position.

L<sub>max</sub> : The measured maximum luminance of all measurement position

# 14. ENVIRONMENTAL ABSOLUTE MAXIMUM RATINGS

| ITEM                  | SYMBOL | CONDITIONS     | CRITERION                   |

|-----------------------|--------|----------------|-----------------------------|

| OPERATING TEMPERATURE | TOPR   | -20°C ~+70°C   | NO DEFECT IN DISPLAYING AND |

|                       | TOTK   | -20 C - 170 C  | OPERATIONAL FUNCTION        |

| STORAGE TEMPERATURE   | TSTG   | -30°C∼+80°C    | NO DEFECT IN DISPLAYING AND |

| STORAGE TEMI ERATORE  | 1510   | -50 C 10 180 C | OPERATIONAL FUNCTION        |

| HUMIDITY              | _      | See Note       | WITHOUT CONDENSATION        |

Note: Test condition:

1) Temperature and humidity: if no specification, temperature set at  $25+/-2^{\circ}$ C, and humidity set at 60+/-5% RH.

2)Operating state: all the tests to which the samples subject should be in operating condition.

| <b>KELIADILIIIIIE</b>           |                                                                                                                                                                                                                               |                                                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| ITEM                            | CONDITIONS                                                                                                                                                                                                                    | CRITERION                                        |

| Operating                       | HIGH TEMPERTURE +70°C 120HRS                                                                                                                                                                                                  | No defect in displaying and operational          |

| Temperature                     | LOW TEMPERTURE -20°C 120HRS                                                                                                                                                                                                   | function                                         |

| Storage                         | HIGH TEMPERTURE +80°C 120HRS                                                                                                                                                                                                  | No defect in displaying and operational          |

| Tempereature                    | LOW TEMPERTURE -30°C 120HRS                                                                                                                                                                                                   | function                                         |

| High Humidity &<br>high Temp    | 50℃ 90%RH 120HRS                                                                                                                                                                                                              | No defect in displaying and operational function |

| Vibration                       | <ul> <li>Operating Time: 30 minutes exposure for each direction (X,Y,Z)</li> <li>Sweep Frequency: 10~55Hz (1 min)</li> <li>Amplitude: 1.5mm</li> </ul>                                                                        | No defect in displaying and operational function |

| Thermal Shock                   | $-25^{\circ}C(30\text{mins}) \leftrightarrow +75^{\circ}C(30\text{mins}) 50 \text{ cycles}$                                                                                                                                   | No defect in displaying and operational function |

| Package laminative<br>load test | Atmospheric pressure:86kPa~106kPa,<br>Temperature:15°C~35°C,<br>Humidity:20%~75%<br>Test machine speed:10mm/min<br>The package laminative load on<br>Sample carton: The weight of a box of<br>production(Kg) multiply 8*2*24H | No defects in display and operational functions  |

# **15. RELIABILITY TEST**

| Packing Drop Test | Droping from a height of 1m onto concrete<br>surface (1 corner, 3 edges, 6 faces) | No defect in appearance |

|-------------------|-----------------------------------------------------------------------------------|-------------------------|

| Life Time         | 50,000H                                                                           |                         |

NOTE: The samples must be free from defect before test, must be restore at room condition at least for 2 hours after reliability test before any inspection.

Each item need 8pcs at least for testing before qualification.

#### **16. THE STANDARD OF INSPECTION**

#### 16-1 SAMPLING PLAN

Unless there is other agreement, sampling plan for incoming inspection should follow GB2828-2003.

16-1-1 Lot size: Quantity per shipment as one lot (different model as different lot .)

- 16-1-2 Sampling type: Normal inspection, single sampling.

- 16-1-3 Sampling level: Level II.

- 16-1-4 Acceptable Quality Level Major defect: AQL=0.40 Minor defect: AQL=0.65 Total defect : AQL=0.65

#### 16-2 PANEL INSPECTION CONDITION

16-2-1 Environment:Room Temperature: 25±5°C.Humidity: 55±5% RH.Illumination:800~1200Lux.

16-2-2 Inspection Distance:  $25 \pm 5$  cm from the inspector to the module.

16-2-3 Inspection Angle: The inspector shall rotate the display 45° from the centerline of the viewing direction to assure that clear cosmetic flaws do not exist on the surface within the view area.

16-2-4 Viewing time for inspector is 6-10 Seconds.

#### 16-3 MODULE INSPECTION STANDARDS

- 16-3-1 Defect definition

- MAJOR: display or functional defects, serious deviation from the specifications, customers can not work properly; Severe skin defects, serious deviation from the specifications, the client does not work properly.

- MINOR: slightly deviate from the specifications, does not affect the product function, but the appearance of an impact on product

- Note: The following standard if no entities are specified, with mm meter.

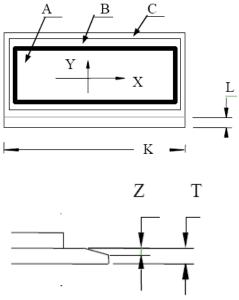

16-3-2 Product area and size code definition

A area: said display active area(characters display)

- B area: says visual area (except A area)

- C area: the unvisual areas.

- T: it says he thickness of the single glass

- L: said glass pin lengths

- K: said product length

- X :said glass long side direction or glass edge direction along the length of the gap

- Y :said glass short side direction or gap with glass edge along the vertical length

Z: the thickness of crack or gap

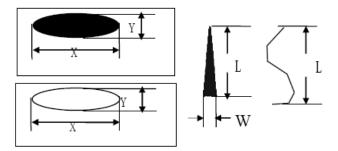

# 16-3-2 Point, line definition

point:  $\Phi = (X + Y) / 2$

The length of the X says point length; Y says point width Line:L says the length of the line; W says line width

16-3-3 Inspection items and specification for appearance(power off)

| No. | Item      | Criterion                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |  |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| 1   | Dimension | Dimension out of the specification                                                                                                                                                                                                                                                                                                                                                                   |                    |  |  |  |  |

|     |           | Dimension out of the specification<br>1. General crack<br>X Y Z<br>$\leq K/8$ $\leq 75\%$ seal<br>$\leq K/8$ $width$ $2. cornerX$ Y Z<br>$\leq K/8$ $\leq 75\%$ seal<br>$\leq K/8$ $\leq 75\%$ seal<br><t<br>3. contact pad crack<br/>X Y Z<br/><math>\leq K/8</math> <math>\leq 1/3</math> <math>Z \leq L/4</math><br/>4. Substrate protuberance and internal crack<br/>X Y <math>X</math> Y</t<br> | AQL<br>1.0<br>2.50 |  |  |  |  |

|     |           | $\leq K/8 \leq L/3$<br>Transfer position crack: $\leq L/5$                                                                                                                                                                                                                                                                                                                                           |                    |  |  |  |  |

# **26**/30

| [                                                                               | 1                        |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

|---------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------|-------------------|----------------------------------------------------|----------------------|---------------|------|-------------------------|--|--|

| 3                                                                               |                          |                                                                          | D                 |                                                    | Acceptable of defect |               |      |                         |  |  |

|                                                                                 |                          | x                                                                        |                   | D                                                  | A/B Area             | C Area        |      |                         |  |  |

|                                                                                 |                          | Ϊ                                                                        | Ι                 | D<0.2                                              | No check             |               |      |                         |  |  |

|                                                                                 | Black dot \<br>White dot |                                                                          | 0.2               | ≤D≤0.3                                             | 2                    | No check      | 2.50 |                         |  |  |

|                                                                                 |                          | Y                                                                        | (                 | ).3 <d< td=""><td>0</td><td></td></d<>             | 0                    |               |      |                         |  |  |

|                                                                                 |                          | X: long diameter Y: shot diameter<br>D: average of diameter D=(X+Y)/2    |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 | Line defect              |                                                                          |                   |                                                    | 1                    |               |      |                         |  |  |

|                                                                                 |                          | L<br>w                                                                   | Length            | Whidth                                             | -                    | ole of defect |      |                         |  |  |

|                                                                                 |                          |                                                                          |                   |                                                    | A/B Area             | C Area        |      |                         |  |  |

|                                                                                 |                          |                                                                          | accept            | W≤0.02                                             | No check             |               | 2.50 |                         |  |  |

|                                                                                 |                          |                                                                          | L≤3               | W≤0.05                                             | 2                    | No check      |      |                         |  |  |

| 4                                                                               |                          | $\bigwedge$                                                              | L≤2.5             | W≤0.05                                             | 2                    |               |      |                         |  |  |

|                                                                                 |                          | L                                                                        | L <u>&gt;</u> 2.3 | W>0.05                                             | 5 As rou             | und type      |      |                         |  |  |

|                                                                                 |                          | > 🖊 🖊 👘                                                                  |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | L: Length W: Width                                                       |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | Defect of polarizer (Scratches, Spot) : According to the limit specimen  |                   |                                                    |                      |               |      |                         |  |  |

| 5                                                                               | Polarizer<br>Bubble      |                                                                          | D<br>D<0.2        |                                                    | Acceptable of defect |               |      |                         |  |  |

|                                                                                 |                          |                                                                          |                   |                                                    | A/B Area             | -             |      |                         |  |  |

|                                                                                 |                          |                                                                          |                   |                                                    | No check             | 011100        | 2.50 |                         |  |  |

|                                                                                 |                          |                                                                          | 0.2≤D≤0.3         |                                                    | 2                    | No check      |      |                         |  |  |

|                                                                                 |                          | Y -                                                                      |                   | .3 <d< td=""><td>0</td><td colspan="2"></td></d<>  | 0                    |               |      |                         |  |  |

|                                                                                 | <b>.</b>                 | 1 7 6                                                                    |                   |                                                    |                      |               |      |                         |  |  |

| -                                                                               | External print           | 1. Transfigure, pin hole: same as segment transfinguer                   |                   |                                                    |                      |               | 2.50 |                         |  |  |

| 6                                                                               | of panel                 | 2. Print width: print width $\geq 1/2$ standard width is acceptable      |                   |                                                    |                      |               |      |                         |  |  |

| 7                                                                               | Silicon glue             | The area of painting silicon glue must cover the ITO circuit.            |                   |                                                    |                      |               |      |                         |  |  |

| 8                                                                               | Defect of<br>PCB         | 1. The char , wrong edition, bresking off circuit, crack and air-logged  |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | orifice are unreceivable for PCB.                                        |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | 2, gold finger of PCB can not be oxidative, smudgy and broken            |                   |                                                    |                      |               |      |                         |  |  |

| 9                                                                               | SMT organ                | $1_{\sim}$ deflexion of component $\leq 1/3$ width of component          |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | 2. Trying to keep dot of soldering tin orbicular                         |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          | 3、Damage、break、wrong assembly and unseal are unreceivable for component. |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 |                          |                                                                          |                   |                                                    |                      |               |      | 4、 comply with IPC-610E |  |  |

|                                                                                 |                          | 10                                                                       | Steel Frame       | 1 Break and distortion are unreceivable for frame. |                      |               |      |                         |  |  |

| $2_{x}$ If there is one nick which can not lead to cast or hole of painting, we |                          |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

| allow that following:                                                           |                          |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

| Length≤5mm;Width≤0.3mm                                                          |                          |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

|                                                                                 | •                        |                                                                          |                   |                                                    |                      |               |      |                         |  |  |

| 10-3-4115 | pection items and    | specification                                                      | tor display dere          | cupor                                      |                     | •                          |          |      |

|-----------|----------------------|--------------------------------------------------------------------|---------------------------|--------------------------------------------|---------------------|----------------------------|----------|------|

| 1         | Electrical<br>Defect |                                                                    | Segment missing Not allow |                                            |                     |                            |          |      |

|           |                      |                                                                    | Segment sho               | ort                                        | Not allo            | W                          |          | 1.0  |

|           | Delett               |                                                                    | Non-displa                | y                                          | Not allo            | w                          |          |      |

|           |                      | 1、Pin hole                                                         |                           | · · · · ·                                  |                     | 1                          |          |      |

| 2         | Pin hole             |                                                                    | $ \land \downarrow $      |                                            | width               | Acceptable of defect       |          |      |

|           |                      | Ъ                                                                  |                           |                                            | W<0.4               | D≤0.2 & D≤1/2W             |          |      |

|           |                      | B                                                                  |                           |                                            | W≥0.4               | D≤0.25 & D≤1/3W            |          | 2.50 |

|           |                      |                                                                    | <b>A</b>                  | *D=(A+B)/2 D≤0.1 acceptable                |                     |                            |          | 2.50 |

| 3         | Display<br>pattern   | л                                                                  | н. н.                     |                                            | Width               | Acceptable of defect       |          |      |

|           |                      |                                                                    |                           | <u> </u>                                   | W<0.4               | $C_{\chi}$ D $G \leq 1/2W$ |          |      |

|           |                      |                                                                    |                           |                                            | W≥0.4               | C, D, G≤0.2                |          |      |

|           |                      |                                                                    |                           |                                            |                     |                            |          | 1.0  |

|           |                      |                                                                    |                           |                                            |                     |                            |          |      |

|           |                      | W: Design dimension $C_{\infty}$ D: discrepant dimension $G= E-F $ |                           |                                            |                     |                            |          |      |